闩锁效应、ESD保护、天线效应

目录

闩锁效应

latch up

CMOS电路中,存在寄生的三极管PNPN,它们相互影响在VDD与GND间产生一低阻通路,形成大电流,烧坏芯片这就是Latch up,又称栓锁效应。

产生原因

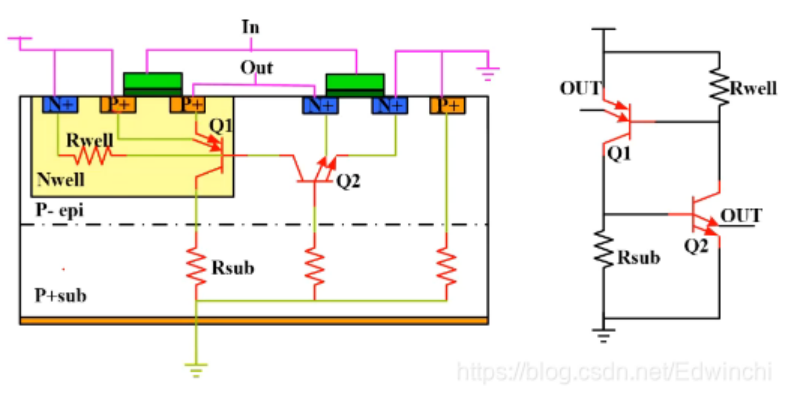

在CMOS工艺中制作的N管和P管间会存在寄生的BJT(PNPN);如下(以N井CMOS工艺制作的反相器为例),N管和P管间存在一个纵向的PNP,和一个横向的NPN。

寄生三极管

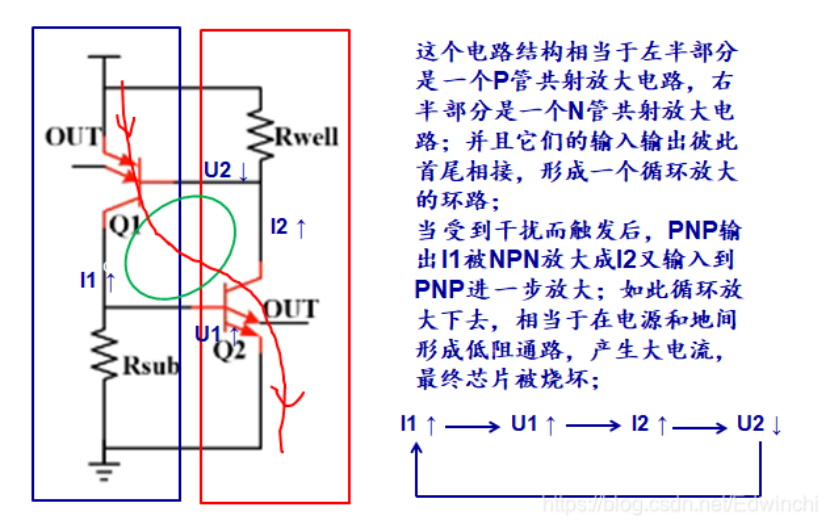

正常工作情况下,三极管是截止的;不会发生Latch up; 当受到外界来自电源,I/O,ESD静电泄放的干扰时,使得其中一个三极管导通后,将反馈到另一个三极管也导通,由于这两个三极管的输入输出是彼此首尾相接,因此形成一个不断循环放大的环路,电流在这个结构里面不断放大,最终超过芯片承受范围,使得芯片被烧坏

寄生三极管电流回路

避免的方法

工艺制造时: 采用重掺杂的衬底(降低Rsub,减小放大环路增益) 采用轻掺杂的外延层(阻止侧向漏电流从纵向PNP到低阻衬底的通路) 使用绝缘隔离槽(SOI绝缘体上硅工艺可彻底消除闩锁效应)

版图设计时: 多打接触孔,接触孔尽量靠近active有源区(降低Rwell,Rsub) 使用Guard ring(一方面降低Rwell,Rsub,一方面阻止载流子到达BJT基极) NMOS靠近GND,PMOS靠近VDD并保持足够距离,降低SCR触发的可能;

ESD保护

静电效应

芯片突然受到高电压低电流的刺激,容易使得芯片被损坏。

产生原因

三种产生模型: 人体接触 带静电的人手触摸芯片

机器接触 制造过程中,与机器接触

自产生电荷 已封装芯片在组合或运输过程中产生电荷

三种模式的电荷不同,作用时间也不同

避免的方法

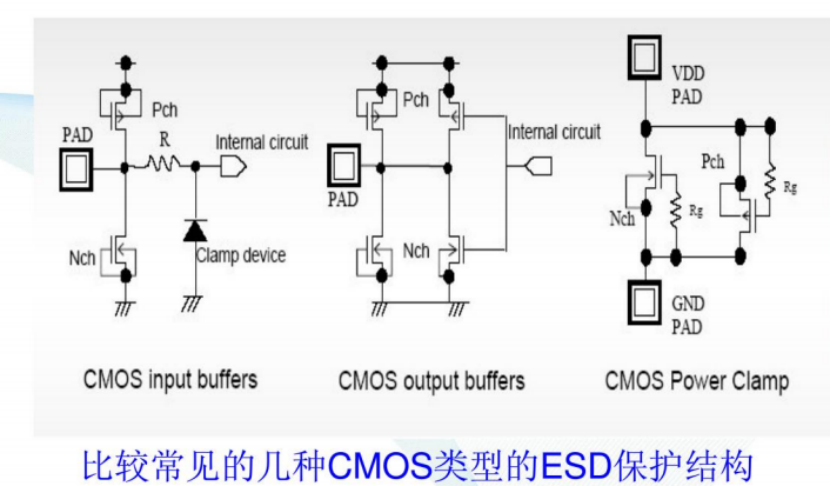

- 增加芯片的抗静电能力 在芯片的pin引脚增加ESD防护电路可以增加芯片对ESD静电的防护能力,但代价是增加了很多芯片面积(ESD器件通常很大一个)

ESD保护电路

- 在接触的时候尽量避免静电,如:在防静电操作台上操作芯片

天线效应

process antenna effect(PAE)

在芯片的蚀刻过程钟,容易出现电荷积累击穿mos管,导致部分mos管的性能出现损失。

产生原因

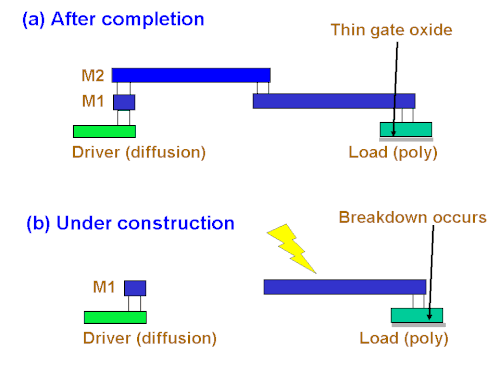

干蚀刻(etch)需要使用很强的电场驱动离子原浆,在蚀刻gate poly和氧化层边的时候,电荷可能积累在gate poly上,并产生电压足以使电流穿过gate的氧化层,虽然这种状况通常不会PAE破坏gate氧化层,但会降低其绝缘程度。这种降低程度于gate氧化层面积内通过的电荷数成正比。每一poly区积累的正电荷与它的面积成正比,如果一块很小的gate氧化层连接到一块很大的poly图形时,就可能造成超出比例的破坏,因为大块的poly区就像一个天线一样收集电荷,所以这种效应称为天线效应,天线效应也会发生在source/drain的离子植入时。

避免的方法

尽量避免画一条很长的线

消除天线效应的方法主要是设法降低接到gate的poly面积。在poly接至gate增加一个metal跳线,即减小了接至gate的poly与gate氧化层的面积之比,起到消除天线效应的作用。

天线效应

① 向上跳层,将面积违例的金属层分成多段,以达到减小”天线”面积的目的 ② 在有天线效应违例的net上挂反向的antenna diode以泄放金属层收集到的电荷。 ③插入buffer,减小net长度达到减小“天线”面积的目的。

文档信息

- 本文作者:Kingdmzhen

- 本文链接:https://icci.ink/2025/07/10/ana-%E7%89%88%E5%9B%BE%E6%95%88%E5%BA%94/

- 版权声明:自由转载-非商用-非衍生-保持署名(创意共享3.0许可证)